在當今信息時代,數字集成電路(IC)構成了電子設備的核心,從智能手機到數據中心,無處不在。而硬件描述語言(HDL)作為連接抽象設計思想與具體物理實現的橋梁,在其中扮演著至關重要的角色。其中,Verilog HDL因其簡潔的C語言風格、強大的建模能力和廣泛的支持,已成為工業(yè)界與學術界進行數字系統(tǒng)設計的主流語言之一。《Verilog HDL數字集成電路設計原理與應用(第二版)》一書,正是系統(tǒng)學習和掌握這一關鍵技術的經典指南。

本書的核心內容緊密圍繞數字集成電路設計的完整流程展開。它首先從Verilog HDL的基礎語法入手,清晰地講解模塊(Module)、端口(Port)、數據類型(如wire、reg)、運算符及行為級建模(always、initial塊)等基本概念。與第一版相比,第二版通常會更注重對最新語言標準(如IEEE Std 1364-2005)特性的闡釋,并強化了對可綜合代碼風格(RTL級描述)的指導,確保設計能夠被主流的綜合工具有效地映射到目標工藝庫。

在原理層面,該書深入探討了如何利用Verilog進行組合邏輯與時序邏輯的建模。讀者將學會如何描述多路選擇器、編碼器、寄存器、計數器以及有限狀態(tài)機(FSM)等基本數字電路模塊。更重要的是,本書將設計原理與硬件思維相結合,強調代碼風格對最終電路面積、速度和功耗的影響,引導讀者避免常見的建模陷阱,如鎖存器的無意生成、仿真與綜合的不匹配等。

“應用”是本書的另一大重點。它超越了單純的語法教學,系統(tǒng)地介紹了基于Verilog的現代數字IC設計方法學。這包括:

- 層次化設計與模塊化方法:如何構建復雜系統(tǒng)的層次結構,實現設計復用。

- 測試平臺的構建:詳細講解如何編寫驗證用的testbench,包括時鐘生成、激勵施加、響應監(jiān)控和結果自動比對,這是保證設計功能正確的關鍵。

- 可綜合設計與設計約束:深入講解如何編寫能被綜合工具理解的RTL代碼,并初步引入時序約束的概念,為后端物理設計奠定基礎。

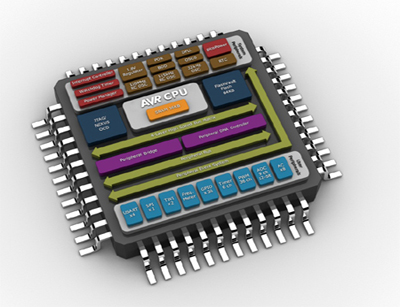

- 設計案例研究:通過CPU子系統(tǒng)、通信接口(如UART)或數字信號處理(DSP)單元等實際案例,將分散的知識點串聯起來,展示從規(guī)格定義、模塊劃分、Verilog編碼、功能仿真到初步綜合的完整項目流程。

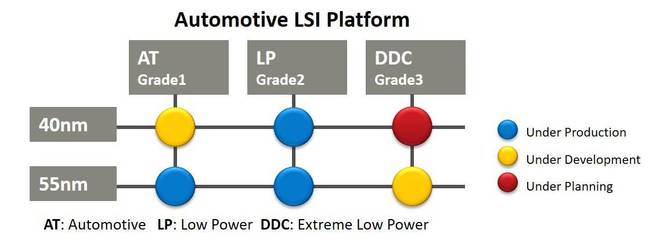

第二版通常會根據技術發(fā)展,增加或強化對前沿設計方法和挑戰(zhàn)的討論,例如低功耗設計技術(時鐘門控、多電壓域)、面向可測性設計(DFT)的基本概念,以及使用Verilog進行簡單FPGA原型驗證的流程簡介。這些內容使讀者不僅掌握語言工具,更能理解工業(yè)級芯片設計的全貌。

總而言之,《Verilog HDL數字集成電路設計原理與應用(第二版)》不僅僅是一本Verilog語法手冊,更是一部貫通設計原理、工程實踐與前沿方法的綜合性教程。它為電子工程、微電子等相關專業(yè)的學生和初入行業(yè)的工程師提供了堅實的理論基礎和實踐指引,是踏入數字集成電路設計殿堂的一把寶貴鑰匙。通過系統(tǒng)學習,讀者能夠建立起從軟件描述到硬件實現的思維范式,為參與高性能處理器、高速通信芯片、智能AI加速器等尖端集成電路的研發(fā)工作做好充分準備。