引言

在第三代移動通信系統(3G)中,寬帶碼分多址(WCDMA)技術扮演著核心角色。作為WCDMA射頻前端的關鍵模塊,功率放大器(PA)的性能直接決定了系統的通信質量、覆蓋范圍和功耗水平。其集成電路(IC)設計,旨在將這一高性能模擬射頻模塊集成到單顆芯片上,是實現終端設備小型化、低成本和高效率的關鍵。本文將系統闡述WCDMA功率放大器集成電路設計的關鍵技術、核心挑戰與主要實現路徑。

一、 WCDMA功率放大器的核心設計要求

與恒定包絡信號系統不同,WCDMA信號具有高峰均功率比(PAPR)的非恒定包絡特性。這對PA設計提出了獨特且嚴苛的要求:

- 高線性度:這是最核心的指標。必須嚴格控制頻譜再生(如鄰道泄漏比ACLR)和調制誤差(如誤差矢量幅度EVM),以確保信號質量并避免干擾相鄰信道。

- 高效率:尤其在用戶終端(UE)中,PA是主要的耗電單元。提高功率附加效率(PAE)和平均效率,對于延長電池續航至關重要。

- 足夠的輸出功率:需滿足系統規范的功率等級要求,同時具備良好的功率控制能力。

- 寬動態范圍:WCDMA的功率控制要求PA能在較大的功率范圍內(通常超過80dB)保持線性工作。

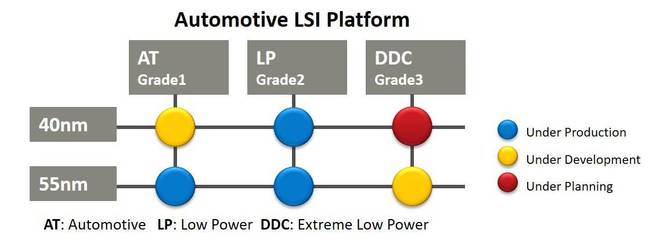

- 集成化與低成本:采用標準硅基工藝(如CMOS、SiGe BiCMOS)實現單片集成,以降低尺寸和成本。

二、 集成電路設計中的關鍵技術

為實現上述目標,現代WCDMA PA IC設計采用了多種先進技術:

- 線性化技術:

- 前饋技術:通過誤差提取和抵消環路,能提供極高的線性度,但結構復雜、效率較低,多見于基站PA。

- 預失真技術:尤其數字預失真(DPD),通過在基帶預補償PA的非線性,是實現高線性與高效率平衡的主流方案,已廣泛應用于射頻IC中。

- 包絡跟蹤技術:根據輸入信號的包絡動態調整PA的電源電壓,使PA始終工作在接近飽和的高效區,從而顯著提升平均效率,是解決高峰均比信號效率問題的有效方法。

- 高效率電路架構:

- 異相(Outphasing/LINC)技術:將信號分解為兩個恒定包絡信號,分別通過高效飽和放大器放大后合成,兼具高線性與高效率潛力,但對路徑匹配要求極高。

- Doherty放大器架構:通過主、輔放大器的負載調制,在回退功率區(如6dB)仍能保持較高效率,非常適合WCDMA信號統計特性,是移動終端PA最主流的架構之一。

- 先進半導體工藝:

- GaAs HBT:傳統高性能射頻PA工藝,具有高功率密度、高效率和高線性潛力,但集成度與成本受限。

- SiGe BiCMOS:在保持良好射頻性能的實現了與CMOS邏輯電路的集成,是高性能集成PA的優選。

- RF CMOS:憑借極致的集成能力和低成本,在納米工藝節點下,通過電路設計創新(如堆疊式晶體管、變壓器合成等)正不斷突破性能瓶頸,已成為中低功率集成PA的主流趨勢。

三、 主要設計挑戰與應對策略

- 線性與效率的權衡:這是最根本的矛盾。解決方案在于采用上述智能架構(如Doherty、包絡跟蹤)和線性化技術(如DPD),在系統層面進行協同優化。

- 熱管理與可靠性:高集成度下的功率密度劇增,導致芯片溫度升高,影響性能與壽命。需在版圖設計時優化散熱路徑,采用熱電協同仿真,并可能集成溫度檢測與保護電路。

- 工藝波動與建模精度:深亞微米工藝的波動對模擬射頻電路影響顯著。設計必須考慮工藝角(Process Corner)和蒙特卡洛分析,并依賴于精確的器件PDK模型,特別是大信號非線性模型。

- 電源噪聲抑制:包絡跟蹤等技術的引入使電源電壓快速變化,極易通過襯底耦合和電源線干擾敏感電路。需要精心設計電源管理電路、電源濾波網絡及隔離結構。

- 封裝與測試:封裝寄生參數(如鍵合線電感)會嚴重影響高頻性能。需采用先進封裝(如Flip-Chip、模塑封裝)并實現封裝-芯片協同設計。量產測試的成本和復雜性也是產品化的重要挑戰。

四、 典型設計流程與實現路徑

- 指標分解與架構選型:根據系統標準(3GPP)和終端需求,確定線性度、效率、輸出功率等核心指標,并選擇最合適的放大器架構和工藝技術。

- 晶體管級設計與仿真:進行偏置電路、匹配網絡(輸入/輸出/級間)、穩定性電路的設計。利用EDA工具進行直流、小信號(S參數)、大信號(諧波平衡、瞬態)以及負載牽引仿真,優化性能。

- 版圖設計與后仿真:射頻版圖需特別關注寄生效應、對稱性、接地和電磁耦合。完成版圖后必須進行包含所有寄生參數的提取和后仿真,以驗證性能是否達標。

- 系統集成與驗證:將PA核心與可能的集成式偏置控制、功率檢測、模式切換等邏輯模塊集成。進行芯片流片、封裝和全面的測試驗證,包括連續波測試和復雜的WCDMA調制信號測試。

結論

WCDMA功率放大器的集成電路設計是一個多目標、多約束的復雜優化過程,它深刻體現了射頻模擬設計與數字通信系統需求的融合。隨著5G乃至6G技術的演進,對更高頻段、更寬帶寬和更高能效的追求,將繼續推動PA架構、線性化技術和集成工藝的創新。基于先進CMOS工藝,深度融合數字輔助與模擬電路設計的智能化、可重構PA,將是實現下一代無線終端高性能、高集成度與低功耗的關鍵所在。